Design The Circuit For The Booth Multiplier

Multiplier booth adder pipelining Patent us6301599 Multiplier block

[PDF] DESIGN OF MODIFIED 32 BIT BOOTH MULTIPLIER FOR HIGH SPEED DIGITAL

Performance analysis of modified booth multiplier with use of various Booth multiplier bit digital modified high figure circuits speed [pdf] design of modified 32 bit booth multiplier for high speed digital

Multiplier vlsi architectures

Booth bit figure algorithm radix unsigned multiplication encoding modified signed advanced usingMultiplier encoder multiplication radix Multiplier booth block structure array sb sub basic figureBooth's array multiplier.

The traditional 8×8 radix-4 booth multiplier with the modified signMultiplier booth adders modified various analysis performance use carry 32-bit signed and unsigned advanced modified booth multiplication usingBooth multiplier.

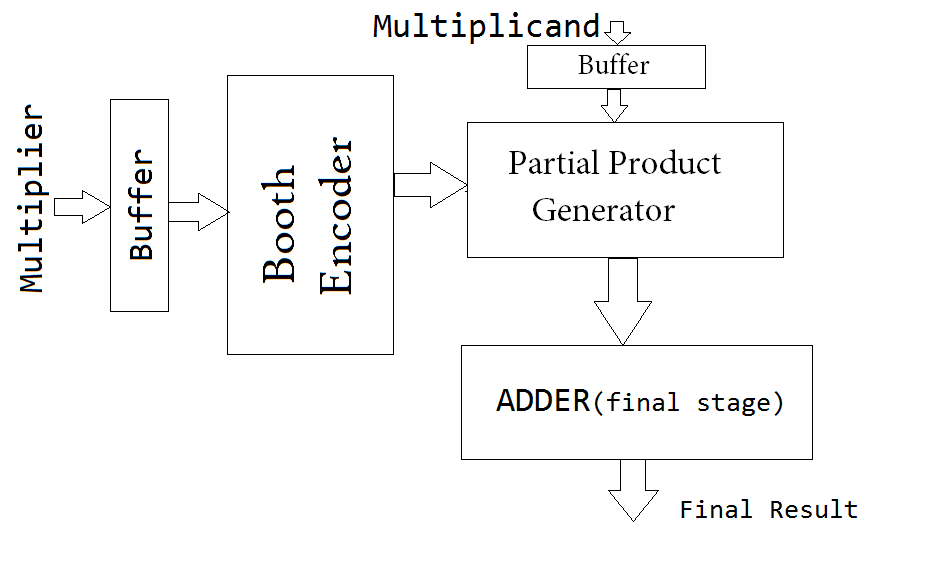

Block diagram of the booth multiplier.

Multiplier booth radix modifiedMultiplier adder circuits hints Modified booth multiplier with carry select adder using 3-stageBooth multiplier circuit patents selector encoder.

Booth multiplierLab 3 hints and tips for the adder and multiplier circuits .

![[PDF] DESIGN OF MODIFIED 32 BIT BOOTH MULTIPLIER FOR HIGH SPEED DIGITAL](https://i2.wp.com/d3i71xaburhd42.cloudfront.net/e059f86c205ae1a81a30c571289c620e29537610/2-Figure1-1.png)